Xilinx Vitis Core Development Kit旨在为用户提供高级设计功能和优势,获得突破性的新算法,模块化设计,提供高级综合工具,告别全程手动创建,规范定位,提供广泛的库支持,设计和优化重用、IP子系统重用、集成自动化和加速设计等优势,加速过程,提高生产力,将是高性能,使用简单的功能和聚合在系统中。

软件功能

一、高级设计功能

以下是用于加速高级设计的Vivado™ML功能的快速概述。单击其他选项卡以获取完整的功能详细信息。

1、Vitis高级合成工具

当今在人工智能、无线、医疗、国防和消费类应用中使用的高级算法比以往任何时候都更加复杂。Vitis™高级综合工具是所有Vivado™版本中的免费升级,无需手动创建等效的RTL设计,即可将C++规范直接定位到AMD可编程器件中,从而加速IP创建。VitisHLS工具支持Vitis和Vivado设计环境,使软件和硬件设计人员能够通过以下方式加速内核或IP创建:

算法描述、具有定点或浮点整数的数据类型规范以及接口(FIFO、存储器、AXI4)的抽象

广泛的库,包括对任意精度数据类型、流和矢量化数据类型的内置支持

指令驱动、架构感知综合,具有高QoR

快速实现QoR,可与手动编码的RTL相媲美

使用C/C++测试台仿真和自动VHDL或Verilog仿真以及测试台生成加速验证

自动使用AMD片上存储器和DSP元件,包括浮点型

2、知识产权集成商

Vivado™ML版通过提供业界首个即插即用的IP集成设计环境及其IP集成器功能,打破了RTL设计生产力的高原。

VivadoIP集成商提供图形化和基于Tcl的按结构校正的设计开发流程。它提供了一个设备和平台感知的交互式环境,支持关键IP接口的智能自动连接,一键式IP子系统生成,实时DRC和接口更改传播,并结合强大的调试能力。

在IP之间建立连接时,设计人员在抽象的“接口”而不是“信号”级别工作,大大提高了生产力。通常,这是使用行业标准的AXI4接口,但IP集成商也支持数十种其他接口。

在接口层面工作,设计团队可以快速组装复杂的系统,利用使用VitisHLS、ModelComposer、AMDSmartCore和LogiCORE™™IP、联盟成员IP以及您自己的IP创建的IP。通过利用VivadoIPI和HLS的组合,与RTL方法相比,客户可节省高达15倍的开发成本。

3、动态功能交换(DFX)

动态函数交换是通过下载部分位文件来动态修改逻辑块的能力,同时剩余逻辑继续运行而不会中断。AMDDFX技术允许设计人员即时更改功能,无需完全重新配置和重新建立链路,从而显著增强了FPGA和SoC提供的灵活性;它是基于平台的设计流程的关键功能,尤其是Alveo加速器卡。使用动态功能交换可以让设计人员迁移到更少或更小的器件,降低功耗,并提高系统的可升级性。通过仅加载任何时间点所需的功能,更有效地利用芯片。

4、使用抽象外壳快速编译

摘要Shell是一种新技术,可以快速编译复杂和大型设计。它允许用户在设计中定义可独立编译的可重构模块。用户可以选择要修改和重新编译的设计部分,而无需重新编译整个设计。

与传统编译相比,Shell的平均编译时间减少了5倍,最高可达17倍。此功能还允许用户在设计中定义多个可以并行编译的模块。

5、Vitis™ModelComposer

Vitis™ModelComposer是一款基于模型的设计工具,可在MathWorksMATLAB®和Simulink®环境中实现快速设计探索,并通过自动代码生成加快AMD设备上的生产速度。您可以设计算法,并使用高级性能优化块进行迭代,并通过系统级仿真验证功能正确性。Vitis模型编排通过自动优化将您的设计转变为生产质量的实施。该工具提供了一个包含200多个HDL、HLS和AI引擎模块的库,用于在AMD设备上设计和实现算法。它还支持将自定义HDL、HLS和AI引擎代码作为块导入到工具中。Vitis模型编辑器包括AMDDSP系统生成器的所有功能,自2020.2起不再作为独立工具提供。

在Vitis模型编辑器中,您可以:

使用针对AI引擎和可编程逻辑的优化模块创建设计。

可视化和分析仿真结果,并将输出与使用MALTAB®和Simulink®生成的黄金参考进行比较。

无缝协同仿真AI引擎和可编程逻辑(HLS、HDL)模块。

自动生成代码(AI引擎数据流图、RTL、HLSC++)和设计测试平台。

将自定义HLS、AI引擎和RTL代码作为块导入。

二、验证

以下是用于验证的VivadoML功能的快速概述。单击其他选项卡以获取完整的功能详细信息。

1、模拟流程

Vivado™设计套件提供一系列设计输入、时序分析、硬件调试和仿真功能,所有这些功能都包含在单一先进的集成设计环境(IDE)中。此流程可满足所有受支持的模拟器的集成和企业验证需求。

Vivado可为完全集成的Vivado仿真器和3RD派对高清模拟器。与流程的后期阶段相比,在设计周期早期花在仿真上的时间有助于及早发现问题,并显著缩短周转时间。

为了提高用户验证环境的灵活性,Vivado既支持集成环境,又提供用于外部验证设置的脚本。

VivadoIDE支持所有主要仿真器,集成模式适用于交互式仿真用户,脚本模式适用于高级验证工程师。

Aldec-Active-HDL®&Riviera-PRO®、CadenceXcelium®Simulator、SiemensEDA–ModelSim®&Questasim®、SynopsysVCS®和AMDVivadoSimulator

2、模拟流程

Vivado™设计套件提供一系列设计输入、时序分析、硬件调试和仿真功能,所有这些功能都包含在单一先进的集成设计环境(IDE)中。此流程可满足所有受支持的模拟器的集成和企业验证需求。

Vivado可为完全集成的Vivado仿真器和3RD派对高清模拟器。与流程的后期阶段相比,在设计周期早期花在仿真上的时间有助于及早发现问题,并显著缩短周转时间。

为了提高用户验证环境的灵活性,Vivado既支持集成环境,又提供用于外部验证设置的脚本。

VivadoIDE支持所有主要仿真器,集成模式适用于交互式仿真用户,脚本模式适用于高级验证工程师。

Aldec-Active-HDL®&Riviera-PRO®、CadenceXcelium®Simulator、SiemensEDA–ModelSim®&Questasim®、SynopsysVCS®和AMDVivadoSimulator

3、验证IP

AMD的验证IP(VIP)产品组合使用户能够在仿真环境中轻松、快速、有效地验证和调试其设计。验证IP核是专门构建的验证模型,其目标是确保正确的互操作性和系统行为。EDA行业的公司为基于标准的接口(AXI,PCIe,SAS,SATA,USB,HDMI,ENET等)开发VIP。使用VIP的优势包括提高设计质量和由于可重用性而缩短的调度时间。

AMDVIP内核是基于SystemVerilog的仿真模型,可通过ARM许可断言提供完整的AXI协议检查,支持所有主要仿真器,并免费包含在Vivado中。AMD提供VIP,用于使用AXI组件级(AXI-MM、AXI_Stream)和处理系统(Zynq™7000)设计的设计。

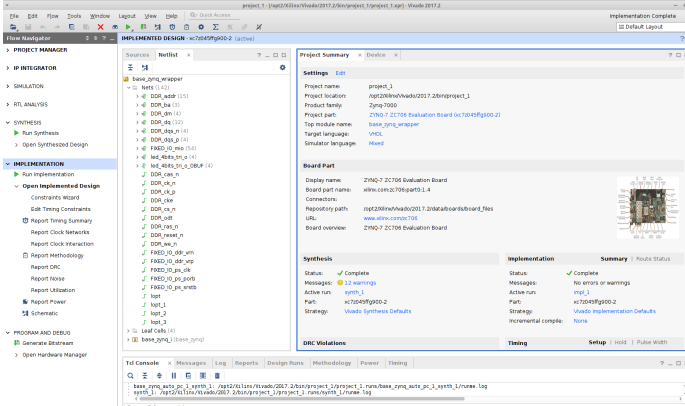

三、实现

以下是Vivado™ML实施功能的快速概述。单击其他选项卡以获取完整的功能详细信息。

1、实现

Vivado实现方案是AMD器件的布局和布线工具,可从合成网表生成比特流和器件镜像。实施支持创建各种尺寸的平台和定制设计,从最小的MPSoC到包含数百万个逻辑单元的最大单片和堆叠硅互连技术(SSIT)设备。Vivado实施基于最先进的分区、放置和路由算法构建,这些算法由基于机器学习的预测器指导。ML模型的应用允许实施在更短的时间内实现更高的结果质量(QoR),并准确预测路由延迟和拥塞。实施由Xilinx设计约束(XDC)驱动,以满足Vivado项目和Tcl脚本中性能、利用率、功耗和综合工作的设计目标。

实施支持所有操作模式,从易于使用的按钮模式到复杂的定制Tcl配方,用于处理具有最严格性能要求的设计。可以在任何编译阶段对时序、利用率、功耗和其他设计质量指标进行详细分析:放置前、放置后和布线后。还可以使用设计检查点(DCP)文件在任何编译阶段保存和恢复设计数据库,并且可以相应地可视化和约束设计。

2、实现

Vivado实现方案是AMD器件的布局和布线工具,可从合成网表生成比特流和器件镜像。实施支持创建各种尺寸的平台和定制设计,从最小的MPSoC到包含数百万个逻辑单元的最大单片和堆叠硅互连技术(SSIT)设备。Vivado实施基于最先进的分区、放置和路由算法构建,这些算法由基于机器学习的预测器指导。ML模型的应用允许实施在更短的时间内实现更高的结果质量(QoR),并准确预测路由延迟和拥塞。实施由Xilinx设计约束(XDC)驱动,以满足Vivado项目和Tcl脚本中性能、利用率、功耗和综合工作的设计目标。

实施支持所有操作模式,从易于使用的按钮模式到复杂的定制Tcl配方,用于处理具有最严格性能要求的设计。可以在任何编译阶段对时序、利用率、功耗和其他设计质量指标进行详细分析:放置前、放置后和布线后。还可以使用设计检查点(DCP)文件在任何编译阶段保存和恢复设计数据库,并且可以相应地可视化和约束设计。

3、设计方法

当与Vivado一起使用时,UltraFast方法有助于定义适当的约束,有助于正确驱动工具和分析结果,并提高整体生产力。UltraFast设计方法集合了Vivado专家多年的经验,以及他们在突破工具和技术极限的客户设计设计方面取得的成功设计经验。

4、自动时序收敛

作为Vivado超快方法的补充,是实现时序收敛自动化的独特方法。除了最佳实践之外,Vivado专家还通过成功完成最具挑战性的设计积累了大量解决方案。这些解决方案往往是程序性的,如超快方法时序收敛参考中所述。Vivado中的自动时序收敛更进一步,根据特定的时序故障执行这些步骤,然后为每个特定问题生成交钥匙解决方案。这些解决方案消除了审查工具报告、制定可能的解决方案以及编译每个解决方案以审查结果并可能迭代无数次以接近时序的冗长手动过程,从而使所有专业水平的硬件设计人员受益。

5、智能设计运行

智能设计运行(IDR)是一种用于时序收敛的按钮流,需要最少的用户干预。IDR通过利用基于规则和机器学习(ML)驱动的功能,将智能构建到设计实施过程中。

IDR是使用基于ML的策略预测开发的,该预测利用基于60,100+设计价值的训练数据的000+自定义策略。

IDR还使用:

基于ML的拥塞估计,用于确定路由中的热点并预测路由器行为以避免拥塞

基于ML的延迟估计,有助于复杂路由的延迟预测

AMDUltraScale™、UltraScale+™和Versal™设备支持IDR。